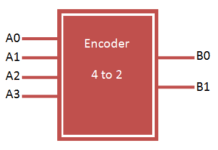

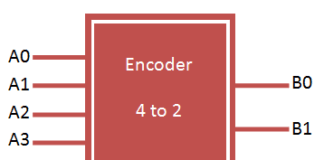

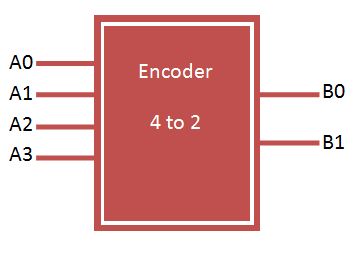

Binary Encoder

Encoders, as the name suggest, encodes a larger bit of information into a smaller bit value. 4 to 2 encoder has 4 input lines and 2 output lines. Encoder can be easily constructed using basic logic gates.

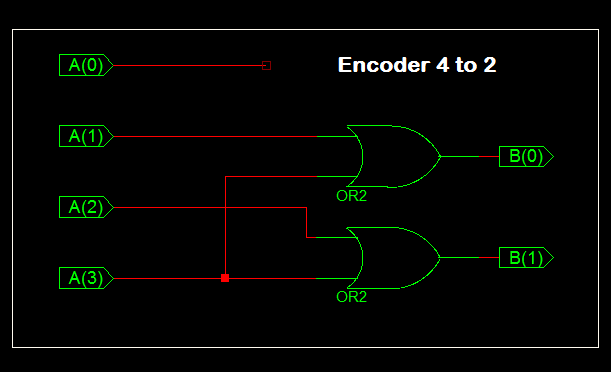

4 to 2 encoder design using logic gates

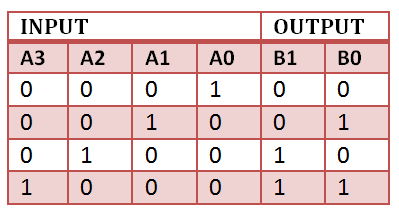

Truth Table for 4 to 2 encoder

VHDL Code for 4 to 2 encoder can be done in different methods like using case statement, using if else statement, using logic gates etc.

VHDL Code for 4 to 2 encoder using case statement

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity encoder is

port(

a : in STD_LOGIC_VECTOR(3 downto 0);

b : out STD_LOGIC_VECTOR(1 downto 0)

);

end encoder;

architecture bhv of encoder is

begin

process(a)

begin

case a is

when “1000” => b <= “00”; when “0100” => b <= “01”; when “0010” => b <= “10”; when “0001” => b <= “11”; when others => b <= “ZZ”;

end case;

end process;

end bhv;

VHDL Code for 4 to 2 encoder using if else statement

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity encoder1 is

port(

a : in STD_LOGIC_VECTOR(3 downto 0);

b : out STD_LOGIC_VECTOR(1 downto 0)

);

end encoder1;

architecture bhv of encoder1 is

begin

process(a)

begin

if (a=”1000″) then

b <= “00”;

elsif (a=”0100″) then

b <= “01”;

elsif (a=”0010″) then

b <= “10”;

elsif (a=”0001″) then

b <= “11”;

else

b <= “ZZ”;

end if;

end process;

end bhv;

VHDL Code for 4 to 2 encoder using logic gates

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity encoder2 is

port(

a : in STD_LOGIC_VECTOR(3 downto 0);

b : out STD_LOGIC_VECTOR(1 downto 0)

);

end encoder2;

architecture bhv of encoder2 is

begin

b(0) <= a(1) or a(2);

b(1) <= a(1) or a(3);

end bhv;